# Exploiting Multi-core Systems for Parallel Network Simulation

Von der Fakultät für Mathematik, Informatik und Naturwissenschaften der RWTH Aachen University zur Erlangung des akademischen Grades eines Doktors der Ingenieurwissenschaften genehmigte Dissertation

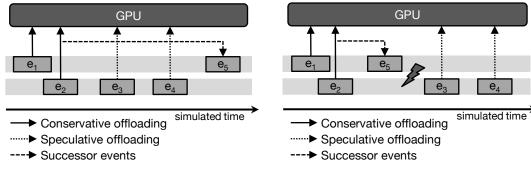

vorgelegt von

Dipl.-Inform.

Georg Johannes Kunz

aus Emmerich, Deutschland

Berichter:

Prof. Dr.-Ing. Klaus Wehrle Prof., Phd. George Riley

Tag der mündlichen Prüfung: 01.03.2013

Diese Dissertation ist auf den Internetseiten der Hochschulbibliothek online verfügbar.

### **Abstract**

Discrete event simulation constitutes a fundamental methodology in the design, development, and evaluation process of communication systems. Despite their abstract nature, simulation models often exhibit considerable computational complexity, resulting in extensive simulation runtimes. To counteract the runtime demand of complex simulation models, *parallel* discrete event simulation distributes the workload of a simulation model across multiple processing units. Traditionally, parallel discrete event simulation focused on investigating large scale system models utilizing distributed computing clusters.

In the last decade, however, two developments have fundamentally changed the established state-of-the-art in parallel discrete event simulation. First, multi-core systems have become the de facto standard hardware platform for desktop and server computers. In contrast to distributed computing clusters, multi-core systems provide different hardware characteristics, notably shared memory. Second, the focus of interest in the research community shifted from wired to wireless communication systems. Contrary to wired networks the simulated network entities are tightly coupled due to detailed modeling of physical layer and wireless channel effects, thereby hindering efficient parallelization. This thesis addresses the challenges resulting from these two developments by designing algorithms and tools to enable and support efficient parallel simulation of tightly coupled systems on multi-core systems. In particular, we make four distinct contributions:

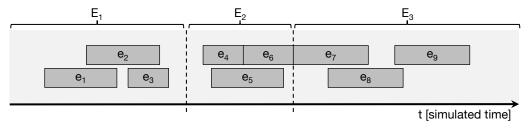

Our first contribution is *parallel expanded event simulation*, a modeling paradigm extending discrete events with durations that span a period in simulated time. The resulting *expanded events* form the basis for a conservative synchronization scheme that considers overlapping expanded events eligible for parallel processing. We furthermore put these concepts into practice by implementing HORIZON, a parallel expanded event simulation framework specifically tailored to multi-core systems.

The durations carried by expanded events provide a deeper insight into event dependencies. Yet, they typically do represent the true dependencies among events. Hence, our second contribution, *probabilistic synchronization*, exploits the globally shared memory space of multi-core systems to observe the behavior of a simulation at runtime and learn accurate dependencies between events. Three different heuristics subsequently exploit the dependency information to guide speculative event execution.

While the previous two contributions focus on speeding up individual simulation runs, our third contribution exploits the massively parallel processing power of GPUs to reduce the runtime demand of entire parameter studies. To this end, we develop a multi-level parallelism scheme that bridges the gap between the fundamentally different processing paradigms underlying expanded event simulation and GPUs.

Finally, the performance of any parallelization scheme heavily depends on the structure of a given simulation model. Hence, we specify a *performance analysis methodology* that enables model developers to identify and eliminate performance bottlenecks in simulation models. In combination, our four contributions provide the means for efficient parallel simulation on multi-core systems.

## Kurzfassung

Ereignisbasierte Simulation stellt ein grundlegendes Werkzeug im Entwicklungsund Evaluationsprozess von Kommunikationssystemen dar. Trotz eines abstrakten Modellierungskonzepts weisen akkurate Simulationsmodelle oftmals eine erhebliche Berechnungskomplexität auf, welche wiederum zu beträchtlichen Ausführungszeiten der Simulation führt. Parallele ereignisbasierte Simulation wirkt dem Zeitbedarf komplexer Simulationsmodelle entgegenwirken, indem die Arbeitslast eines Simulationsmodells auf mehrere Berechnungseinheiten aufgeteilt wird. Der Fokus paralleler ereignisbasierter Simulation lag dabei traditionell auf der Untersuchung hochverteilter Systeme, z.B. Peer-to-Peer Netzwerke, mittels verteilter Rechnerverbünde.

Zwei Entwicklungen führten jedoch in den vergangenen zehn Jahren zu weitreichenden Veränderungen der Voraussetzungen, die den etablierten Parallelisierungstechniken zu Grunde liegen. Erstens sind Mehrkernprozessoren zum de-facto Standard für Server und Arbeitsplatzcomputer geworden. Im Gegensatz zu verteilten Rechnerverbünden weisen Mehrkernsysteme andere Hardwareeigenschaften auf, wie etwa durch Rechenkerne gemeinsam verwendbaren Speicher. Zweitens verlagerte sich der Interessensfokus in der Forschung von drahtgebundenen zu drahtlosen Kommunikationssystemen. Im Unterschied zu drahtgebundenen Netzen besteht aufgrund der detailgetreuen Modellierung des drahtlosen Kanals eine enge Kopplung zwischen den Komponenten drahtloser Netze. Diese Arbeit befasst sich mit den Herausforderungen, die aus diesen beiden Entwicklungen erwachsen. Konkret werden in dieser Arbeit vier Lösungsansätze erarbeitet und vorgestellt:

Beim ersten Lösungsansatz handelt es sich um "parallel expanded event simulation", ein Modellierungsparadigma welches zeitdiskrete Ereignisse derart erweitert, dass sie eine Periode in simulierter Zeit überspannen. Die daraus resultierenden erweiterten Ereignisse bilden die Basis für ein konservatives Parallelisierungsschema, welches eine effiziente Synchronisation eng gekoppelter Systeme ermöglicht.

Unter Ausnutzung der Eigenschaften von Mehrkernsystemen, insbesondere des gemeinsam verwendbaren Speichers, zielt ein probabilistischer Synchronisationsalgorithmus darauf ab akkurate Abhängigkeitsrelationen zwischen Ereignissen zur Simulationslaufzeit zu bestimmen. Diese Abhängigkeitsrelationen erlauben folglich eine spekulative parallele Ausführung nicht überlappender erweiterter Ereignisse.

Während die beiden vorigen Ansätze eine Laufzeitreduktion einzelner Simulationsläufe abstreben, befasst sich der dritte Lösungsbeitrag mit der Laufzeitreduktion von Parameterstudien, die mehrere einzelne Simulationsläufe umfassen. Hierzu nutzt ein *Mehrebenen-Parallelisierungsverfahren* die hochparallele Rechenleistung von Grafikprozessoren und überbrückt die grundlegenden architekturellen Unterschiede zwischen Grafik- und Standardprozessoren.

Zu guter Letzt umfasst der vierte Lösungsansatz ein Leistungsanalyseverfahren, welches Entwicklern von parallelen Simulationsmodellen ermöglicht Leistungsengpässe zu identifizieren. In ihrer Kombination legen diese vier Lösungsansätze die Grundlage für eine effiziente parallele ereignisorientierte Simulation von Kommunikationssystemen auf Mehrkernsystemen.

## **Acknowledgments**

The genesis of this thesis was significantly influenced by students, colleagues, friends, and family.

I would like to express my sincere gratitude to my both my advisers, Klaus Wehrle and James Gross. Klaus paved the way for my PhD not just by teaching me how to create posters and slides, but also by ensuring that the center of my personal life could remain in Aachen. Moreover, his valuable feedback, advice, and ideas laid the foundations for this thesis. James openly welcomed me into his group, despite my evidently poor knowledge of physical layer modeling and statistical methods. His dedication and the fruitful discussions revolving around my research topic contributed considerably to this thesis. He never grew tired motivating me throughout periods of doubt and uncertainty. I would also like to thank George Riley for reviewing my thesis and for acting as second opponent.

I am very grateful for the opportunity to work with four highly talented students. Their tremendous efforts actively shaped the contributions of this thesis and the corresponding implementations. Remembering long and lively discussions, I would like to thank Mirko Stoffers for his influence on probabilistic synchronization and HORIZON, Simon Tenbusch for his enthusiasm regarding optimization problems, Daniel Schemmel for his programming skills and CUDA knowledge, and Marc Peiter for his work on load balancing algorithms.

Over the years, my colleagues have been a constant source of valuable input and personal distraction. I owe Hanno Wirtz a special "thank you" for gracefully enduring my diversions into the non-research related corners of the Internet. Similarly, Raimondas Sasnauskas is not just a motivating role model of a successful researcher to me, but also a close friend. Many thanks to Oscar Puñal and Donald Parruca for taking good care of me at UMIC as well as allowing me to use and benefit from their simulation models. Moreover, I'd like to thank René Hummen for his friendship throughout our time as diploma and PhD students. Stefan Götz showed me how to approach and solve research problems in a structured manner and Tobias Heer was an example in discipline and dedication to me. I'd like to thank Olaf Landsiedel for recommending me as a PhD student to Klaus and for his interest in sharing and discussing new ideas. In addition, a big "thank you" goes to Dirk, Elias, Florian, Hamad, Henrik, Ismet, Janosch, Jó, Marco, Martin, Matteo, Nico, and all members of ComSys and MNP for the scientific adventures and for having a nice time with you.

Finally, my project "PhD" was only made possible by the unconditional support of my family. By believing in me, Rolf, Lili, and Julia provided the motivation for pursuing my PhD. Above all, I am very grateful to Simone for accepting my last minute decision to start a PhD in Aachen, for sacrificing many evenings of leisure time during paper and thesis writing phases, and for pushing me through all periods of doubts throughout my PhD.

# **Contents**

| 1 | Intr | Introduction |                                                           |    |  |  |

|---|------|--------------|-----------------------------------------------------------|----|--|--|

|   | 1.1  | Proble       | em Analysis                                               | 2  |  |  |

|   |      | 1.1.1        | Performance Factors of Parallel Discrete Event Simulation | 2  |  |  |

|   |      | 1.1.2        | Problem Statement                                         | 3  |  |  |

|   |      | 1.1.3        | Research Questions                                        | 5  |  |  |

|   | 1.2  | Contr        | ibutions                                                  | 6  |  |  |

|   |      | 1.2.1        | Interplay of Contributions and Research Questions         | 7  |  |  |

|   |      | 1.2.2        | Relationship of Contributions                             | 8  |  |  |

|   | 1.3  | Outlin       | ne                                                        | 9  |  |  |

| 2 | Par  | allel D      | Discrete Event Simulation                                 | 11 |  |  |

|   | 2.1  | Discre       | ete Event Simulation                                      | 11 |  |  |

|   |      | 2.1.1        | Nomenclature                                              | 11 |  |  |

|   |      | 2.1.2        | Execution Model                                           | 12 |  |  |

|   |      | 2.1.3        | Modeling Principle                                        | 13 |  |  |

|   |      | 2.1.4        | Comparison with other Evaluation Methodologies            | 13 |  |  |

|   | 2.2  | Goals        | and Challenges of Parallelization                         | 15 |  |  |

|   |      | 2.2.1        | The Need for Parallel Discrete Event Simulation           | 15 |  |  |

|   |      | 2.2.2        | Approaches to Parallelization                             | 16 |  |  |

|   |      | 2.2.3        | Challenges of Parallel Event Execution                    | 18 |  |  |

|   | 2.3  | Conce        | epts of Parallel Discrete Event Simulation                | 19 |  |  |

|   |      | 2.3.1        | Workload Partitioning                                     | 19 |  |  |

|   |      | 2.3.2        | Causal Correctness                                        | 21 |  |  |

|   |      | 2.3.3        | Synchronization Schemes                                   | 22 |  |  |

|   |      | 2.3.4        | Parallel Event Execution Environments                     | 28 |  |  |

|   | 2.4  | Parall       | el Discrete Event Simulation Frameworks                   | 29 |  |  |

|   |      | 2.4.1        | Overview                                                  | 29 |  |  |

|   |      | 2.4.2        | Comparison and Conclusion                                 | 32 |  |  |

| 3 | Par | allel <i>E</i> | Expanded Event Simulation                        | 35 |  |

|---|-----|----------------|--------------------------------------------------|----|--|

|   | 3.1 | Motivation     |                                                  |    |  |

|   | 3.2 | Proble         | em Analysis                                      | 37 |  |

|   |     | 3.2.1          | Properties of Wireless System Models             | 37 |  |

|   |     | 3.2.2          | Modeling Time-Spans in Discrete Event Simulation | 38 |  |

|   |     | 3.2.3          | Goals                                            | 39 |  |

|   | 3.3 | Parall         | el Expanded Event Simulation                     | 39 |  |

|   |     | 3.3.1          | General Idea                                     | 40 |  |

|   |     | 3.3.2          | Expanded Events                                  | 40 |  |

|   |     | 3.3.3          | Sequential Expanded Event Execution Model        | 42 |  |

|   |     | 3.3.4          | Parallel Expanded Event Execution Model          | 45 |  |

|   |     | 3.3.5          | Determining Event Durations                      | 47 |  |

|   |     | 3.3.6          | Related Work                                     | 49 |  |

|   |     | 3.3.7          | Summary                                          | 51 |  |

|   | 3.4 | The H          | Iorizon Simulation Framework                     | 51 |  |

|   |     | 3.4.1          | Centralized Parallelization Architecture         | 52 |  |

|   |     | 3.4.2          | Implementation of the Horizon Framework          | 59 |  |

|   |     | 3.4.3          | Related Work                                     | 61 |  |

|   |     | 3.4.4          | Evaluation                                       | 63 |  |

|   |     | 3.4.5          | Summary                                          | 73 |  |

|   | 3.5 | Minim          | nizing the Parallelization Overhead              | 74 |  |

|   |     | 3.5.1          | Analyzing the Parallelization Overhead           | 75 |  |

|   |     | 3.5.2          | Goals and Achievements                           | 77 |  |

|   |     | 3.5.3          | Efficient Event Scheduling                       | 77 |  |

|   |     | 3.5.4          | Related Work                                     | 80 |  |

|   |     | 3.5.5          | Evaluation                                       | 82 |  |

|   |     | 3.5.6          | Summary                                          | 88 |  |

|   | 3.6 | Discus         | ssion and Limitations                            | 89 |  |

|   |     | 3.6.1          | Parallel Expanded Event Simulation               | 89 |  |

|   |     | 3.6.2          | Horizon                                          | 90 |  |

|   | 3.7 | Concl          | usions                                           | 91 |  |

| 4 | $\operatorname{Pro}$ | stic Synchronization | 93                                             |     |

|---|----------------------|----------------------|------------------------------------------------|-----|

|   | 4.1                  | Motiv                | ation                                          | 93  |

|   | 4.2                  | Proble               | em Analysis                                    | 95  |

|   |                      | 4.2.1                | Limitations of Classic Synchronization         | 95  |

|   |                      | 4.2.2                | Complexity vs. Accuracy                        | 97  |

|   | 4.3                  | Relate               | ed Work                                        | 97  |

|   |                      | 4.3.1                | Limiting Optimism By Means of Time Windows     | 97  |

|   |                      | 4.3.2                | Probabilistic Synchronization                  | 98  |

|   |                      | 4.3.3                | Lookahead Extraction                           | 98  |

|   |                      | 4.3.4                | Hybrid Synchronization Schemes                 | 99  |

|   | 4.4                  | Proba                | abilistic Synchronization                      | 99  |

|   |                      | 4.4.1                | Design Goals and General Concept               | 99  |

|   |                      | 4.4.2                | Arrival Pattern Heuristic                      | 100 |

|   |                      | 4.4.3                | Global Order Heuristic                         | 102 |

|   |                      | 4.4.4                | Local Order Heuristic                          | 103 |

|   | 4.5                  | Discus               | ssion                                          | 106 |

|   |                      | 4.5.1                | Relation to Parallel Expanded Event Simulation | 106 |

|   |                      | 4.5.2                | Relation to Horizon                            | 107 |

|   | 4.6                  | Evalu                | ation                                          | 108 |

|   |                      | 4.6.1                | Implementation                                 | 109 |

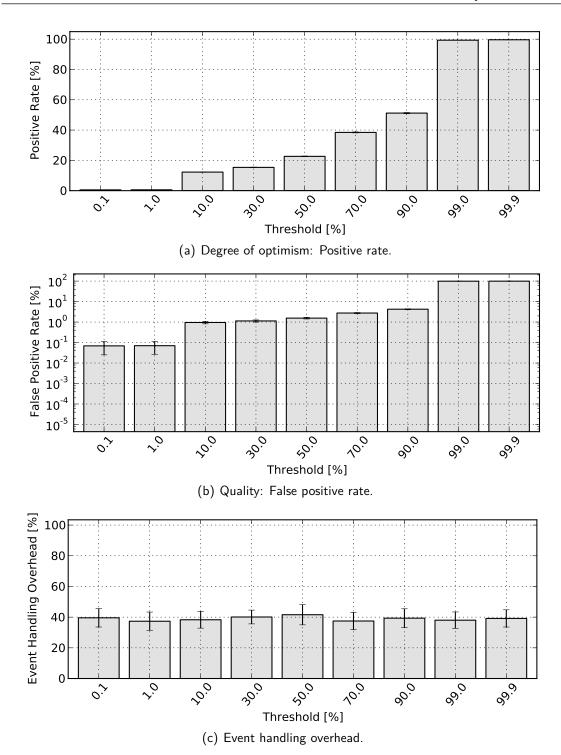

|   |                      | 4.6.2                | Synthetic Benchmarks                           | 109 |

|   |                      | 4.6.3                | Case Study                                     | 115 |

|   |                      | 4.6.4                | Synchronization Phases                         | 118 |

|   | 4.7                  | Concl                | usions                                         | 119 |

| 5 | Мıı                  | lti lov              | el Parallelism on GPUs                         | 121 |

| J | 5.1                  |                      | ation                                          |     |

|   | 5.2                  |                      | enges of Integrating GPUs with PDES            |     |

|   | 0.4                  | 5.2.1                |                                                |     |

|   |                      |                      | Lockstep Execution of Threads                  |     |

|   | FO                   | 5.2.2                | Memory Size, Latency, and Control Overhead     |     |

|   | 5.3                  |                      | ed Work                                        |     |

|   |                      | 5.3.1                | Integrating GPUs with PDES                     |     |

|   |                      | 5.3.2                | Efficient Execution of Parameter Studies       | 127 |

|   | 5.4 | Multi-         | -level Parallelization on GPUs                                         |

|---|-----|----------------|------------------------------------------------------------------------|

|   |     | 5.4.1          | SIMT-compatible workload using External Parallelism 127                |

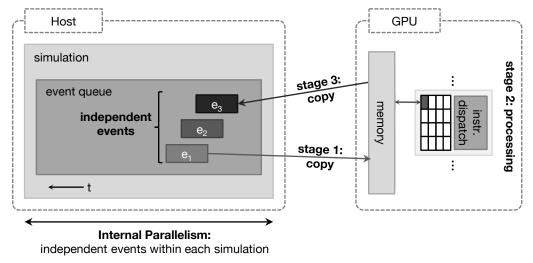

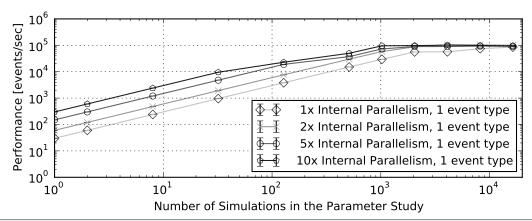

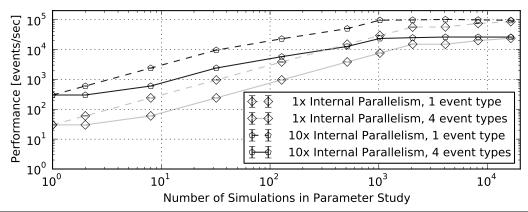

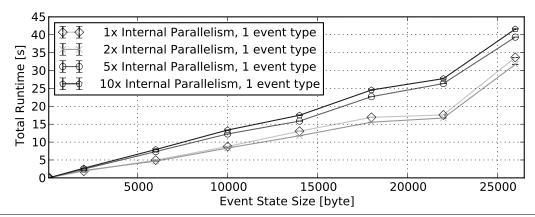

|   |     | 5.4.2          | Hiding Memory Latencies using Internal Parallelism                     |

|   | 5.5 | Discus         | ssion                                                                  |

|   |     | 5.5.1          | Integration of Parallel Expanded Event Simulation 133                  |

|   |     | 5.5.2          | Restrictions of the Programming Environment                            |

|   |     | 5.5.3          | Limited GPU-Memory                                                     |

|   | 5.6 | Imple          | mentation                                                              |

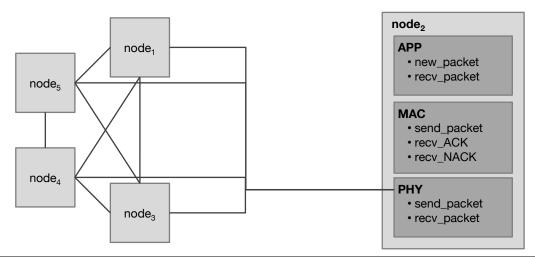

|   |     | 5.6.1          | Programming Interface                                                  |

|   |     | 5.6.2          | Memory Management                                                      |

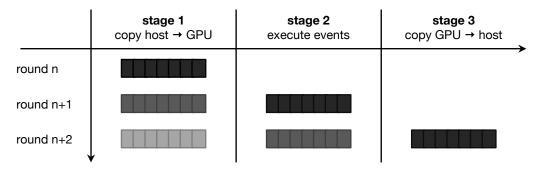

|   |     | 5.6.3          | Pipelined Execution                                                    |

|   | 5.7 | Evalua         | ation                                                                  |

|   |     | 5.7.1          | Synthetic Benchmarks                                                   |

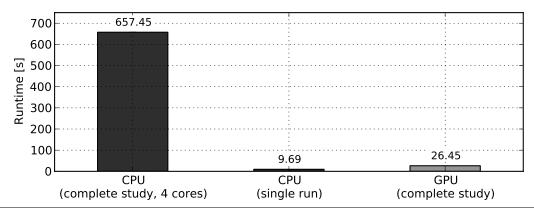

|   |     | 5.7.2          | Case Study                                                             |

|   | 5.8 | Concl          | usions                                                                 |

| 6 | Per | formaı         | nce Analysis of Parallel Expanded Event Simulations 147                |

|   | 6.1 |                | ation                                                                  |

|   | 6.2 | Proble         | em Analysis                                                            |

|   | 6.3 | Related Work   |                                                                        |

|   |     | 6.3.1          | Critical Path Analysis                                                 |

|   |     | 6.3.2          | Synchronization Overhead Estimation                                    |

|   |     | 6.3.3          | Resource-based Performance Analyzers                                   |

|   | 6.4 | Perfor         | mance Analysis Methodology                                             |

|   |     | 6.4.1          | Tracing Simulation Runtime Data                                        |

|   |     | 6.4.2          | Problem Definition                                                     |

|   |     | 6.4.3          | Mixed Integer Linear Program Formulation                               |

|   | 6.5 | Scalab         | pility Improvements                                                    |

|   |     |                |                                                                        |

|   |     | 6.5.1          | Splitting Schedules                                                    |

|   |     | 6.5.1<br>6.5.2 | Splitting Schedules                                                    |

|   |     |                |                                                                        |

|   | 6.6 | 6.5.2<br>6.5.3 | Eliminating Events with Insignificant Processing Times 160             |

|   | 6.6 | 6.5.2<br>6.5.3 | Eliminating Events with Insignificant Processing Times 160 Relaxations |

|    |       | 6.6.2                  | Accuracy                                                                                     | • •   | 164 |

|----|-------|------------------------|----------------------------------------------------------------------------------------------|-------|-----|

|    |       | 6.6.3                  | Scalability                                                                                  |       | 166 |

|    |       | 6.6.4                  | Analyzing Event Schedules for Performance Optimization .                                     |       | 170 |

|    | 6.7   | Discus                 | ssion and Limitations                                                                        |       | 171 |

|    | 6.8   | Concl                  | usions                                                                                       |       | 172 |

| 7  | Sun   | nmary                  | and Conclusions                                                                              | 1     | 175 |

|    | 7.1   | Contr                  | ibutions and Achievements                                                                    |       | 176 |

|    |       | 7.1.1                  | Parallel Expanded Event Simulation                                                           |       | 176 |

|    |       | 7.1.2                  | Probabilistic Synchronization                                                                |       | 177 |

|    |       | 7.1.3                  | Multi-level Parallelism using GPUs                                                           |       | 177 |

|    |       | 7.1.4                  | Performance Prediction and Analysis                                                          |       | 178 |

|    | 7.2   | Applie                 | cation of our Work                                                                           |       | 178 |

|    | 7.3   | Future                 | e Directions                                                                                 |       | 179 |

|    |       | 7.3.1                  | Earliest-Completion-Time-First Scheduling                                                    |       | 179 |

|    |       | 7.3.2                  | $\label{lem:automatic} \mbox{Automatic Configuration of Probabilistic Synchronization} \; .$ |       | 180 |

|    |       | 7.3.3                  | Multi-level Parallelism on GPUs                                                              |       | 181 |

|    | 7.4   | Final                  | Remarks                                                                                      | • • • | 182 |

| Gl | lossa | $\mathbf{r}\mathbf{y}$ |                                                                                              | 1     | 185 |

| Bi | bliog | graphy                 |                                                                                              | 1     | 189 |

# 1

# Introduction

Discrete Event Simulation (DES) constitutes an essential methodology in the design, development, and evaluation process of communication systems. By employing an abstract model, i. e., a software-based implementation of a system under investigation, discrete event simulation provides a controllable and reproducible evaluation tool at low cost. Following the design principle that simulation models should be as accurate as necessary but as simple as possible [Box76], simulation models focus on the relevant characteristics of a system and abstract from the properties irrelevant to the goal of a particular evaluation study.

Despite this abstraction, simulation models often exhibit complex characteristics which are fundamental for correctly representing the systems being evaluated. For instance, wireless communication systems require detailed modeling of the physical effects influencing a wireless transmission, and simulated peer-to-peer networks need to comprise a large number of nodes to accurately capture the behavior of large scale networks. Modeling such characteristics in detail consequently results in complex simulation models and thus extensive simulation runtimes, which in turn hamper the development and evaluation process.

To counteract this effect, the research community developed parallel simulation techniques to harvest the processing power of multiple processing units [Fuj90a, Liu09, Nic96, Per06b]. These techniques traditionally focus on distributed simulations running on computing clusters composed of independent computers. However, such systems are expensive and not easily accessible to model developers and researchers. Parallel Discrete Event Simulation (PDES) is hence not widely adopted by networking researchers for day-to-day simulation, except for specialized applications developed and deployed by specialists [FPP+03, Per05, PPFR03].

Nevertheless, we observe two developments which fundamentally changed the established situation of parallel discrete event simulation over the last decade:

- The proliferation of multi-core computer systems, and

- the shift of focus from wired to wireless networks in the research community.

2 1. Introduction

Multi-core systems have become the de facto standard hardware platform for commodity desktop and server systems, providing simulation developers and researches with ubiquitously available parallel hardware. Specifically, multi-core systems contain one or more processors which in turn comprise multiple processing cores, each appearing as an individual processor to the operating system. However, while the number of cores in these systems increased constantly, the performance of each individual core remained stable [Sut05]. Hence, software aiming to take full advantage of multi-core systems must make use of parallelization techniques [SL05]. As a result, simulation developers and researchers inevitably have to transition from sequential to parallel simulations. However, due to the architectural differences between distributed computing clusters and multi-core systems, existing parallelization techniques do not efficiently utilize multi-core systems. Consequently, we identify the need for new parallelization techniques which are explicitly tailored to the properties of multi-core systems.

At the same time, the networking research community shifted its focus from wired networks to wireless systems. Specifically, the availability of cheap wireless transmission technologies such as IEEE 802.11 or IEEE 802.15.4 sparked extensive research in domains like Mobile Ad-hoc Networks (MANETs), Wireless Mesh Networks (WMNs), and Wireless Sensor Networks (WSNs) [AWK+11, BLKW08]. In contrast to simulation models of wired networks, accurately modeling wireless networks requires a detailed and hence computationally complex representation of the physical effects influencing wireless transmissions. Moreover, due to the broadcast nature of the wireless channel and the small distances between communicating network nodes, the entities in wireless systems are tightly coupled. This tight coupling in turn hinders parallelization of the corresponding simulation models and effectively limits simulation performance [JZT+04, LN02, MB98]. We thus observe the need for new parallelization paradigms that efficiently handle simulation models of tightly coupled systems.

Motivated by these two developments, the goal of this thesis is to develop novel and improve existing parallel simulation techniques that exploit the characteristics of multi-core systems in order to efficiently execute parallel simulation models of tightly coupled systems.

# 1.1 Problem Analysis

Before being able to design parallelization techniques for multi-core systems, we have to establish an understanding of the problem space. To this end, we first analyze the performance factors influencing a parallel discrete event simulation. We then identify the specific problems and research questions addressed in this thesis.

# 1.1.1 Performance Factors of Parallel Discrete Event Simulation

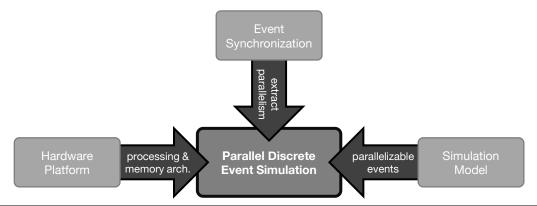

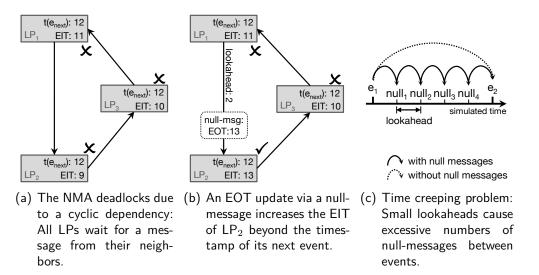

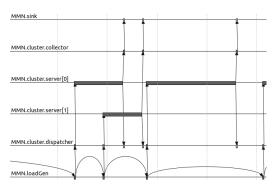

The performance of a parallel discrete event simulation is subject to three factors: i) the event synchronization algorithm, ii) the underlying hardware platform, and iii) the simulation model (see Figure 1.1).

Figure 1.1 Three factors influence the performance of a parallel discrete event simulation:

i) the characteristics of the underlying hardware platform, ii) the ability of the event synchronization algorithm to extract parallelizable events from a simulation model, and iii) the number of parallelizable events provided by a model.

Event Synchronization: In discrete event simulation, events represent changes of the state of a simulation model. The order in which these state changes occur during a simulation naturally influences the results of the simulation. Hence, parallel discrete event simulation employs synchronization algorithms that enforce a correct sequential event execution order among dependent events. Yet, to maximize the performance of a parallel discrete event simulation, synchronization algorithms try to execute a maximum number of independent events in parallel while minimizing the synchronization overhead.

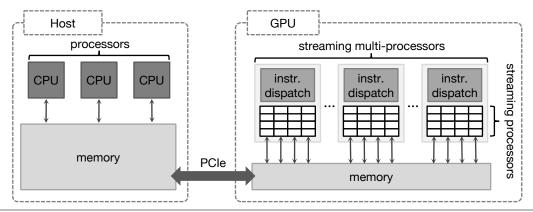

Hardware Platform: A wide range of hardware platforms support parallel execution of simulations, including general purpose platforms such as distributed compute clusters and multi-core systems as well as specialized architectures like vector computers and Graphics Processing Units (GPUs). These platforms exhibit different *characteristics* in terms of memory structure, processing model, and communication overhead. Hence, the design and implementation of a parallel simulation framework has to be tailored to the characteristics of the underlying hardware to maximize performance and efficiency.

**Simulation Model:** A simulation model primarily has to correctly model the system under investigation. However, in order to *foster* efficient parallel execution, it also has to exhibit a *structure* that supports synchronization algorithms in extracting a maximum number of parallelizable events.

Designing an efficient and well performing parallel discrete event simulation requires consideration of all three performance factors. In the next section, we identify shortcomings of the current state-of-the-art with regard to these performance factors.

### 1.1.2 Problem Statement

Given the performance factors of parallel discrete event simulation, we now revisit the initially identified two developments that motivate this thesis: i) the proliferation of multi-core systems, and ii) the research focus on wireless networks. We derive three problem statements from these developments and put them into the context of the performance factors. 1. Introduction

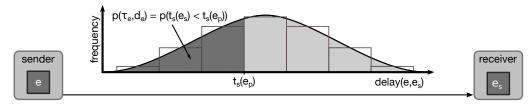

## 1.1.2.1 Lack of Event Dependency Information

The shift of focus from wired networks to wireless systems exposes the inability of discrete event simulation to express dependencies between events. Specifically, parallel discrete event simulation employs synchronization algorithms to ensure the correctness of the simulation results while extracting parallelizable events from a simulation model. Ideally, synchronization algorithms allow parallel processing of all events which do not depend on each other, i.e., which do not modify the same state of the simulation model. A general purpose simulation framework, however, has no knowledge of the semantics of an event and hence the state changes it performs. Instead, the only accessible information to derive dependencies between events is the *time of occurrence* of events. However, in wireless networks, nodes interact at small timescales due to the broadcast nature of the wireless channel and the small distances between communicating network nodes. As a result, the time of occurrence of events fails to accurately reflect event dependencies in such tightly coupled systems  $[JZT^+04, LN02, MB98]$ .

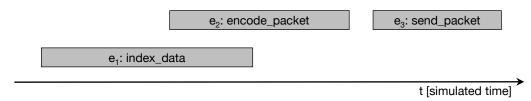

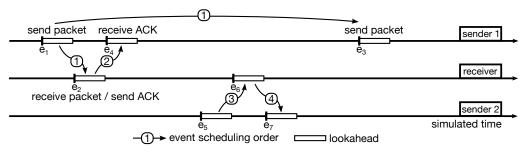

Still, events in a simulation model are often inherently dependent: In discrete event simulation, events happen instantaneously at a single point in time and have no means of representing time spans. Hence, to model processes that span a period of time, e.g., sending and receiving of packets, discrete event simulation utilizes two events: One representing the start of the process and another one indicating the completion of the process. These two events implicitly depend on each other since i) every "start"-event is followed by exactly one "completion"-event, and ii) the "completion"-event will never precede the "start"-event. The event synchronization algorithm, nevertheless, does not know about this relationship because it is missing from the simulation model and hence handles both events individually. It thereby ignores valuable dependency information, resulting in fewer parallelizable events. We thus conclude that discrete event simulation lacks the ability to express the dependency between two such events, thereby hampering efficient event synchronization.

### 1.1.2.2 Unsuitable Event Synchronization Algorithms

By employing techniques rooted in traditional distributed simulation, synchronization algorithms do not fully exploit the capabilities and processing power of multicore systems. In distributed simulation, partitions of a simulation model are distributed across independent computers. Since all partitions of the simulation reside in isolated local memory at the compute nodes, events and synchronization information need to traverse a network interconnecting the nodes. As a result, the communication overhead dominates the total synchronization overhead.

On multi-core systems, however, the performance characteristics of the underlying hardware have changed significantly. A globally shared memory space provides synchronization algorithms with immediate access to the *entire* simulation model, hence enabling a deeper insight into the simulation model and its behavior. Furthermore, fast thread synchronization mechanisms allow for frequent synchronization with low overhead without the need for sending and receiving messages over a network. Moreover, recently emerging specialized multi-core hardware such as GPUs provide massively parallel processing power. However, GPUs implement a

fundamentally different processing model than classic CPUs. This fact needs to be explicitly considered by event synchronization algorithms.

Concluding, we claim that the synchronization algorithms deployed in today's parallel simulation frameworks are deeply rooted in traditional distributed simulation. As a result, they do not make full use of the hardware characteristics of multicore systems, thereby failing to exploit the available processing power. Instead, multi-core systems provide the substrate for developing novel approaches to event synchronization.

## 1.1.2.3 Lack of Development Support

Parallel discrete event simulation is not widely employed today since the development of high-performance parallel simulations is complex and challenging: In addition to correctly modeling the system under investigation, model developers also have to structure the simulation model such that it provides a maximum of parallelizable events. This requires a solid understanding of parallel discrete event simulation and event synchronization. Yet, model developers are typically experts in their particular field of research, but not in parallel discrete event simulation. This lack of experience and knowledge prevents a wide adoption of parallel discrete event simulation.

However, multi-core systems constitute the current and future hardware architecture for desktop and server systems. Since these systems demand parallel programming to fully utilize their processing power, model developers and researchers are forced to employ parallel discrete event simulation. The resulting large yet inexperienced user base of parallel discrete event simulation hence requires dedicated tools to ease the development of parallelizable simulation models. In particular, model developers need performance analysis and prediction tools which provide a deep insight into the behavior of parallel simulations to allow for identifying and eliminating performance bottlenecks.

# 1.1.3 Research Questions

We condense the previous problem analysis in three distinct research questions. It is our goal to provide answers to these questions in the remainder of this thesis.

# Question Q1 - How to improve parallel simulation of tightly coupled systems?

We explore modeling and synchronization schemes that explicitly take the properties of tightly coupled systems, such as wireless networks, into account in order to achieve efficient parallel discrete event simulation.

# Question Q2 - How to efficiently exploit multi-core systems?

We investigate simulation techniques and parallelization schemes for efficiently exploiting multi-core systems and GPUs for parallel discrete event simulation.

# Question Q3 - How to support developers of parallel simulations?

We study means which support model developers in developing efficiently parallelizable simulation models. 1. Introduction

# 1.2 Contributions

We address the aforementioned questions by making four contributions in this thesis:

- i) A modeling paradigm and a corresponding parallelization scheme [KLG<sup>+</sup>10, KLW09, KSGW11] tailored to efficiently handle tightly coupled systems.

- ii) A probabilistic event synchronization scheme [KSGW12b, Sto11] which utilizes shared memory to learn dependencies between events at runtime.

- iii) A multi-level parallelization scheme [KSGW12a, Sch11] exploiting the massively parallel hardware of general purpose GPUs on multi-core machines.

- iv) A performance analysis methodology aiming to support the development process of parallel simulations in order to foster the adoption of parallel simulation among developers and researchers [KTGW11, Ten10].

In the following, we outline the concept of each contribution in more detail.

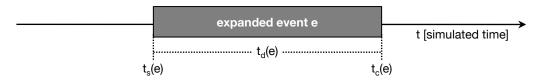

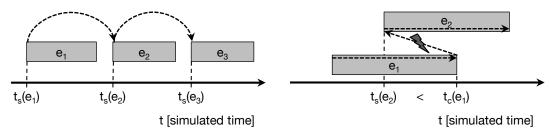

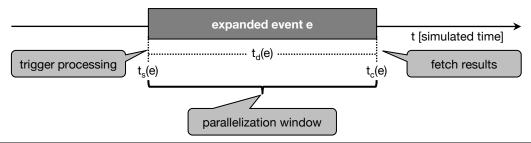

# Contribution C1 - Parallel Expanded Event Simulation

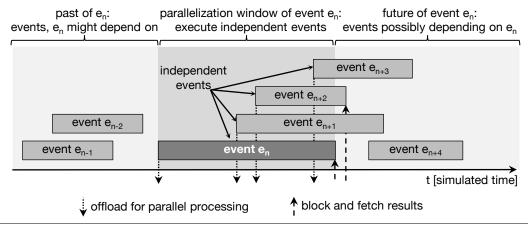

Targeting the lack of dependency information in discrete event simulations, we propose a modeling paradigm that explicitly adds additional timing information to simulation models in order to express dependencies among events. Specifically, the expanded event simulation modeling paradigm assigns durations in simulated virtual time to events [KLG+10, KLW09]. The resulting expanded events represent physical processes that span a period of time. Based on expanded events, we furthermore specify parallel expanded event simulation, a centrally coordinated parallel event execution scheme. This scheme utilizes event durations to identify independent events for parallel execution. We moreover prove that our parallelization scheme ensures the correctness of a parallel simulation run.

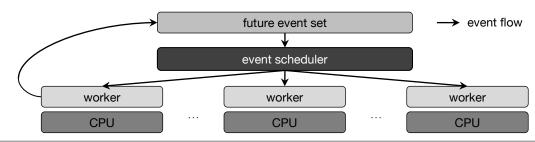

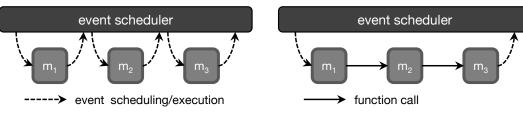

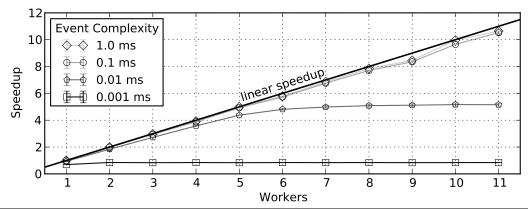

In addition to this conceptual work, we implement the parallel expanded event simulation principle in a state-of-the-art simulation framework. The resulting extended framework, named Horizon, employs a centralized event synchronization architecture that dynamically distributes events eligible for parallel processing to a pool of worker threads. Since performance is key in parallelization, Horizon builds on event handling and thread synchronization algorithms that are specifically tailored to multi-core systems [KSGW11]. Our evaluation illustrates that Horizon achieves significant performance improvements over traditional distributed parallelization.

# Contribution C2 - Probabilistic Event Synchronization

We design a probabilistic synchronization [KSGW12b, Sto11] scheme that exploits shared memory on multi-core systems to collect extensive knowledge of event dependencies at runtime. Three heuristics utilize this dependency information to dynamically decide if a given event should be *speculatively* executed in parallel to other events or not.

This scheme combines the advantages of the two fundamental synchronization paradigms underlying parallel discrete event simulation: Conservative and optimistic synchronization. By switching between conservative and optimistic synchronization on a per event basis, the synchronization scheme is able to extract a larger degree of parallelism from tightly coupled system models than

1.2. Contributions 7

conservative synchronization while limiting the overhead of overly optimistic synchronization. Our evaluation confirms that probabilistic event synchronization outperforms both traditional synchronization schemes as well as previous work on probabilistic synchronization.

### Contribution C3 - Multi-level Parallelization on GPUs

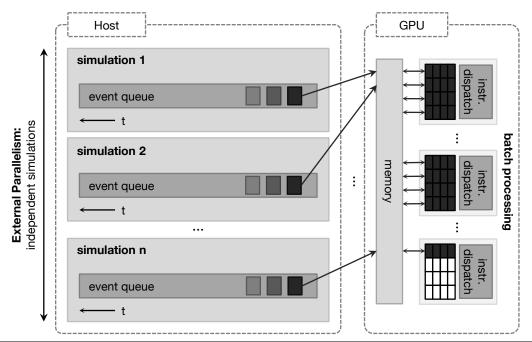

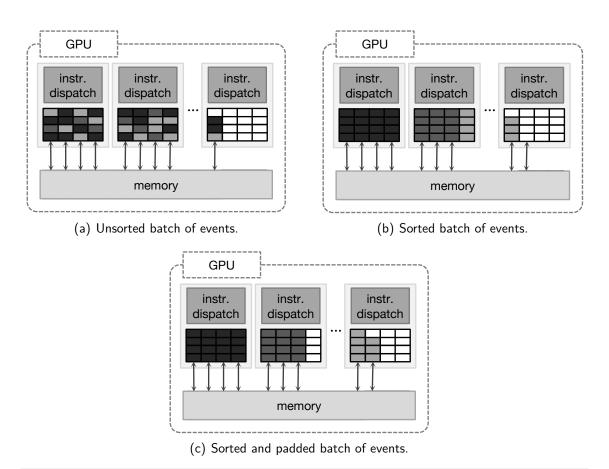

We utilize the highly parallel processing power of GPUs to cost-efficiently reduce the runtime demand of parameter studies. Parameter studies comprise multiple independent simulation runs of the same model using different parameterization to find an optimal configuration of the system under investigation. To efficiently combine GPUs with parallel discrete event simulation despite fundamentally different programming and execution models, we employ a multi-level parallelization scheme [KSGW12a, Sch11]. The scheme utilizes i) external parallelism between the individual simulations of a parameter study to integrate the processing model of GPUs, and ii) internal parallelism among independent events within each simulation to hide the latency between CPU-and GPU-memory. By means of a prototype implementation, we demonstrate significant performance improvements and cost savings over traditional CPU-based parameter studies.

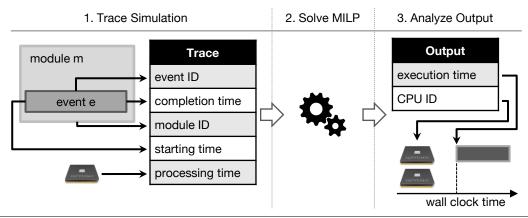

### Contribution C4 - Performance Prediction and Analysis

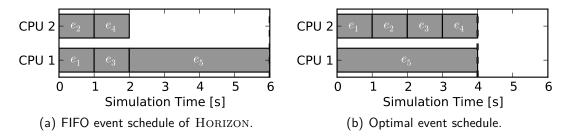

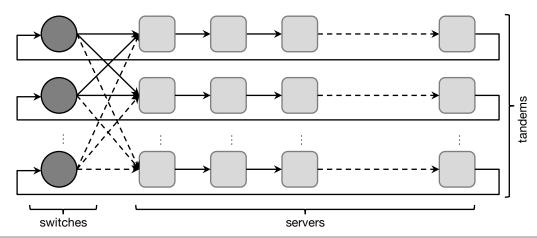

We present a performance analysis methodology that enables model developers to identify performance bottlenecks in parallel expanded event simulations [KTGW11]. Given an event execution trace of an expanded event simulation, the methodology determines an optimal event-to-CPU mapping that minimizes the simulation runtime under consideration of event dependencies and the utilization of a given number of CPUs. By analyzing the resulting event mapping, developers can pinpoint events that prevent parallel execution and cause low CPU utilization.

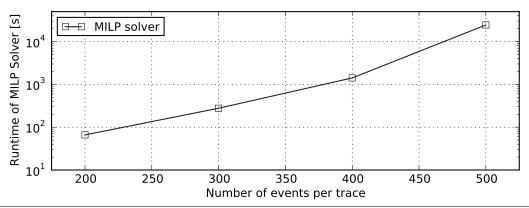

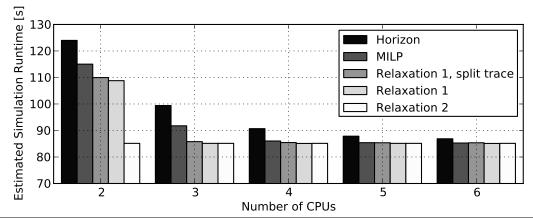

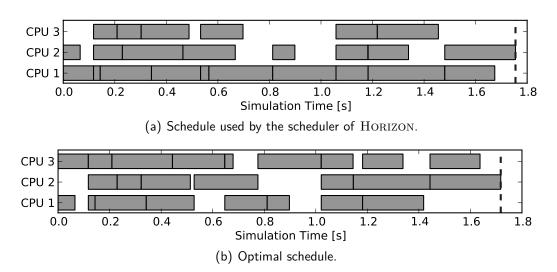

Since this mapping problem is NP-complete [Che90, LK78], we model the parallel expanded event simulation paradigm as a Mixed Integer Linear Program (MILP). As a result, we leave the problem of calculating an optimal event schedule to the efficient heuristics and algorithms of modern MILP solvers. Moreover, to further mitigate the complexity problem, we develop performance optimizations and relaxations of the MILP. These optimizations reduce the scheduling problem on average from exponential to polynomial complexity, thereby making it applicable in practice. We demonstrate that the methodology accurately identifies optimal runtime bounds and performance bottlenecks of parallel expanded event simulations.

These contributions were partially developed in cooperation with students in the context of their Bachelor's and Master's theses [Pei12, Sch11, Sto11, Ten10]. Hence, I'd like to explicitly thank these students for their input and their contributions to this thesis.

# 1.2.1 Interplay of Contributions and Research Questions

The four contributions of this thesis provide answers to the previously identified three research questions. However, there is no simple one-to-one mapping of contributions

1. Introduction

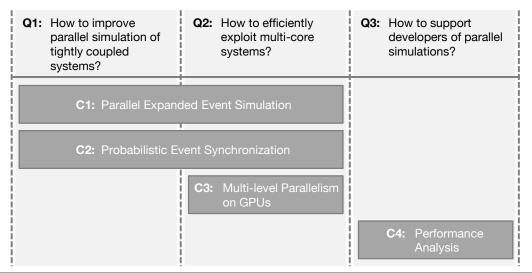

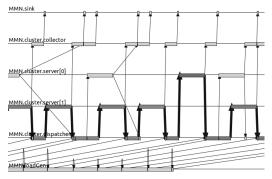

Figure 1.2 Overview showing the interplay of contributions and research questions. Both, parallel expanded event simulation (C1) and Probabilistic synchronization (C2) address multi-core systems as well as efficient simulation of tightly coupled systems. Multi-level parallelization (C3) in turn focuses solely on multi-core systems while our performance analysis methodology (C4) answers the question of development support.

to research questions. Instead, our contributions address the research questions from different perspectives. Figure 1.2 illustrates the interplay of contributions and research questions in this thesis.

Parallel expanded event simulation (C1) addresses both questions Q1 and Q2. While the centralized architecture exploits multi-core computers, expanded events convey dependency information about events in order to handle tightly coupled systems. The probabilistic synchronization scheme (C2) similarly tackles questions Q1 and Q2, yet from a different perspective. It uses shared memory to obtain detailed knowledge of event dependencies which in turn guides speculative event execution to mitigate the performance limitations of tightly coupled systems. Furthermore, multi-level parallelization (C3) utilizes the massively parallel processing power of GPUs which constitute a special-purpose multi-core architecture. The scheme makes heavy use of shared CPU- and GPU-memory, thus contributing an answer to question Q2. Finally, the performance analysis methodology (C4) supports simulation developers in understanding and optimizing the performance of parallel expanded event simulations, thereby giving an answer to question Q3. Throughout this thesis, we compare our contributions to related efforts and illustrate how our approaches deviate from the established state-of-the-art in dedicated related work sections.

# 1.2.2 Relationship of Contributions

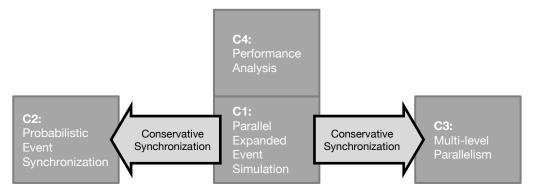

Our four contributions are not isolated but exhibit strong relationships as illustrated in Figure 1.3. Parallel expanded event simulation (C1) constitutes our central contribution. It lays the foundation for our performance analysis methodology (C4) which is designed to accurately reflect the behavior of parallel expanded event simulations. Hence, these two contributions are closely linked.

1.3. Outline 9

Figure 1.3 Relationship of our four contributions. Parallel expanded event simulation (C1) constitutes the core contribution of this thesis, laying the foundation for the performance analysis methodology (C4). Probabilistic synchronization (C2) and multi-level parallelization (C3) are orthogonal to parallel expanded event simulation and hence independent of expanded events. Yet both contributions can utilize parallel expanded event simulation as conservative synchronization scheme.

Furthermore, parallel expanded event simulation seamlessly integrates with probabilistic event synchronization (C2) and multi-level parallelization (C3): In probabilistic event synchronization, parallel expanded event simulation can serve as conservative synchronization scheme. Similarly, multi-level parallelization can make use of parallel expanded event simulation to conservatively identify independent events according to its internal parallelization scheme.

# 1.3 Outline

The structure of this thesis is as follows. In Chapter 2, we lay the foundation of the thesis by introducing the established techniques and the current state-of-the-art in parallel discrete event simulation. Chapter 3 introduces the concept of parallel expanded event simulation. In particular, we define a centralized parallelization scheme, prove its correctness, and evaluate its performance. Subsequently, Chapter 4 presents our probabilistic synchronization scheme. Moreover, we show in Chapter 5 how to efficiently incorporate GPUs in parallel discrete event simulation. In addition to those efforts, we address the challenge of creating efficient parallel simulation models in Chapter 6 by designing and evaluating our performance analysis methodology. Finally, Chapter 7 concludes the thesis by summarizing our contributions and discussing future work.

1. Introduction

# 2

# **Parallel Discrete Event Simulation**

Parallel Discrete Event Simulation (PDES) is the subject of extensive research for more than two decades. Consequently, the literature on PDES comprises a rich set of theoretical and practical results [Fuj90a, Kun10, Liu09, Nic96, Per06b]. This chapter introduces the relevant basics that lay the foundation for this thesis. To this end, we first introduce the fundamental concepts of Discrete Event Simulation (DES) and motivate the need for parallelization. Based on this motivation, we then discuss the key challenges of parallelization, classify basic parallelization techniques, and define relevant terms. Finally, we give a brief overview of state-of-the-art parallel simulation frameworks.

# 2.1 Discrete Event Simulation

The purpose of Discrete Event Simulation (DES) is to model the behavior and the properties of a particular system under investigation, for instance a communication network. Specifically, DES aims at enabling a controllable and repeatable evaluation process at low cost and with short development cycles. It provides the primary means for evaluating complex systems before prototyping and deployment. DES achieves these goals by abstracting from the system under investigation and instead relying on a simplified, purely software based implementation, denoted a *simulation model*.

# 2.1.1 Nomenclature

This thesis clearly distinguishes between the *simulation framework* and the *simulation model*. The simulation framework provides basic functionality for implementing and executing simulation models. Simulation models in turn define the behavior of a system under investigation. To this end, simulation models maintain a state and

represent state changes by means of *events*. In a communication system, for instance, an event might model that a simulated network node sends a packet and increases its sent-packet-counter state variable.

To add a notion of temporal relation to state changes, a discrete event simulation maintains a global virtual time, denoted *simulated time*, that represents the time within a simulation model. Events change the state of the simulation model at *discrete* points in this simulated time. To this end, every event carries a timestamp, specifying its time of occurrence in simulated time, and an *event handler function*. The event handler function is code of the simulation model that modifies the state of the simulation and potentially creates new events with a timestamp equal or larger than the current simulated time. For example, a send-packet-event might create a new event representing the next sending operation at a future point in simulated time. During a simulation, the *Future Event Set (FES)* holds all events available for execution sorted in increasing timestamp order.

Moreover, we define the terms event type and event instance as follows: The type of an event is given by the event handler function and possibly additional metadata. An event instance, in turn, is an incarnation of a unique event type. Drawing a comparison with the terminology of object oriented programming, an event type corresponds to a class definition while an event instance is a particular object created from a class definition. In the remainder of this thesis, we use the term event as synonym for event instance unless explicitly stated otherwise.

Formally, we define the following terms used throughout the remainder of this thesis:

- $E = \{e_1, \dots, e_n\}$  is the finite set of all events occurring in a simulation,

- $F \subseteq E$  is the subset of events in the FES,

- $T \subseteq \mathbb{R}^{\geq 0}$  denotes the virtual simulated time, and

- $t: E \to T$  is a function that assigns a timestamp to each event  $e \in E$ .

Note that F changes over time as events are created and processed. Hence, we can consider F to be a function of time, mapping a given point in simulated time to a subset of E, i. e.,  $F: T \to \mathcal{P}(E)$ . However, we refrain from using this notation in this thesis for the sake of simplicity and to avoid redundancies: Where needed, we explicitly state relevant events in F as  $e \in F$  and denote their timestamps as t(e), thereby indicating the simulated time.

### 2.1.2 Execution Model

The execution model of a discrete event simulation is as follows. An *event scheduler* drives a *simulation run* by continuously i) dequeueing the first event from the FES, ii) setting the simulated time to the timestamp of the event, and iii) executing the event handler function associated with the event.

During execution of the event handler function, the simulated time remains constant, i.e., events happen instantaneously and last zero units in simulated time. Since the FES is sorted with respect to increasing timestamps, simulated time hence advances i) monotonically and ii) in discrete steps. The first property guarantees a *causally correct* execution of the simulation in which the cause (events with an earlier timestamp) always precedes its effect (events with a later timestamp). The

second property decouples simulated time from the continuous notion of real time, called *simulation time*. As a result, simulated time may advance both faster as well as slower than simulation time, depending on the complexity of the model and the processing power of the simulation platform. A simulation run finally ends when either the FES is empty or a predefined termination condition is met.

# 2.1.3 Modeling Principle

The primary modeling principle underlying simulation is abstraction. In line with the famous quote of George Box that "essentially, all models are wrong, but some are useful" [BD87], the goal of a model developer is to design a model of a system under investigation that is as accurate as necessary but as simple as possible. This means in particular, that a simulation model is designed specifically towards the goals of an evaluation study while leaving out details and aspects not relevant to the study.

For instance, in models of wired networks, the physical effects of a transmission are generally ignored since the error rates on a wire are negligibly. In contrast, modeling the physical effects of the wireless channel in wireless networks is imperative for correctness. A further example is headers in simulated network packets. Typically, simulation model abstract from real world technicalities such as bit fields and byte orders when modeling packet headers. Instead, header fields might just be member variables of a C++ packet class. If, however, the simulation contains real code or interacts with real system, utilizing bit-based headers might be necessary.

Along the same line of reasoning, the system parameters as well as the results and statistics generated by a simulation model depend on the properties being studied. Hence, a simulation model should only provide and vary those parameters which are necessary to collect the statistics of interest with respect to the goals of an evaluation study. In conclusion, the goal of abstraction is to limiting the model complexity in order to obtain understandable, maintainable, and verifiable simulation models.

# 2.1.4 Comparison with other Evaluation Methodologies

Simulation plays an integral role in the design and evaluation process of communication systems. Nevertheless, its primary principle – abstraction – is both boon and bane as it allows for fast development as well as abstraction beyond correctness. Hence, simulation constitutes only a single step in a thorough evaluation process [KLW10]. In the following, we briefly introduce three evaluation methodologies complementing simulation and put all methodologies in context.

Analytical Modeling: Based purely on mathematical models, analytical modeling typically exhibits a higher level of abstraction than simulation. Hence, an analytical model represents a specific property of a system by means of a formula, for instance the throughput in TCP [MSMO97, PFTK98]. In contrast, simulation models are usually abstract implementations of a specific protocol that is conceptually similar to a real protocol implementation. As a result, an analytical system model provides a clean, fast, and often provable evaluation

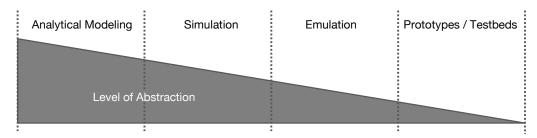

**Figure 2.1** Comparison of the four major evaluation methodologies available for the development of communication systems. The level of abstraction from real-world systems is the highest for analytical models and steady decreases over simulation and emulation towards prototypes and testbeds.

methodology, assuming the problem formulation is efficiently solvable. However, devising an accurate analytical model demands extensive mathematical knowledge and typically relies on strong assumptions. Moreover, representing the involved behavior of distributed systems in a purely mathematical fashion often results in complex and computationally intractable models [GG10].

Emulation: In the context of communication systems, emulation refers to a simulation based evaluation process that involves production code as used in real systems [JM05], or even incorporates real systems in the simulation process [Fal99]. Please note that in other domains, emulation refers to highly accurate simulation models, for instance of hardware and/or software systems [Bel05]. Due to the inclusion of real system components in the network simulation, emulation exhibits a significantly lower level of abstraction than simulation, yielding evaluation results closer to reality. At the same time, however, real components increase the complexity of the evaluation setup and limit scalability in comparison to simulation. Moreover, the simulation has to handle headers of network packets on a bit level, or at least provide functionality to convert real packets to and from an abstract representation used by the simulation.

Prototypes and Testbeds: Testbeds built from prototypes or real systems constitute the means for the final evaluation process of a system before deployment in a production environment. Since prototypes comprise the (almost) finalized hard- and/or software, they provide a precise insight into the system behavior, performance, and implementation bugs. Nevertheless, to aid evaluation, analysis, and debugging, testbeds might employ unobtrusive means of abstraction such as a wired side-channel in a wireless sensor network testbed [ASW05]. The most prominent limitations of testbeds, however, are the cost of purchasing and maintaining a testbed, thereby restricting scalability, as well as a lack of repeatability due to uncontrollable side-effects, thus impeding evaluation and debugging [SPBP06].

Figure 2.1 compares discrete event simulation with the evaluation methods discussed above in terms of the level of abstraction from real world systems. We observe that analytical models exhibit the highest level of abstraction which steadily decreases for simulation and emulation towards prototypes and testbeds.

Unfortunately, the evaluation methods are typically incompatible in terms of programming interfaces. Hence, transitioning between different methods often requires re-implementing the system under investigation. In order to eliminate the need for re-implementations, abstraction layers provide a common programming interface across different evaluation and deployment platforms. As part of our overall work, we contributed to the development of an abstraction layer [LKGW09] targeting protocol development and experimentation [KLGW09].

Due to the high level of abstraction, simulation aims at the initial phase of the development process, allowing for quickly estimating the performance of a system. In practice, however, simulation models exhibit considerable computational complexity, thereby hampering the ability for rapid performance estimation. This thesis investigates parallelization techniques to retain this fundamental property of simulation.

# 2.2 Goals and Challenges of Parallelization

In this section, we first motivate the need for parallel discrete event simulation in greater detail. We then discuss different means of parallelization before formalizing the central challenges of parallel discrete event simulation.

# 2.2.1 The Need for Parallel Discrete Event Simulation

Simulation models must accurately reflect the properties of a given system to allow for correctly investigating its properties. In general, the complexity of the system under investigation carries over to the respective simulation model. As a result, accurate models of complex systems, such as communication systems, exhibit non-trivial computational resource requirements in terms of computing power and memory demands. These resource requirements in turn hamper thorough evaluation studies, e.g., due to extensive runtimes, and hence hinder efficient development and evaluation of new systems.

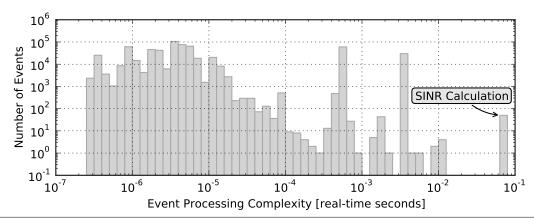

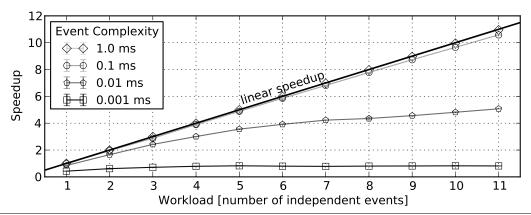

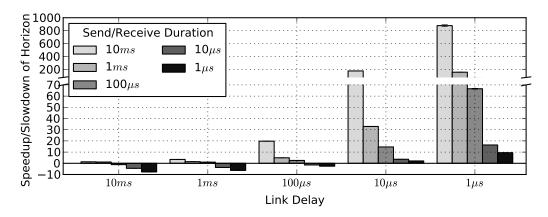

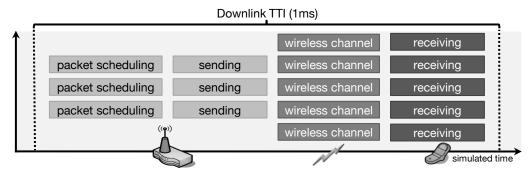

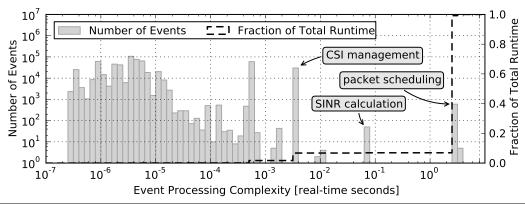

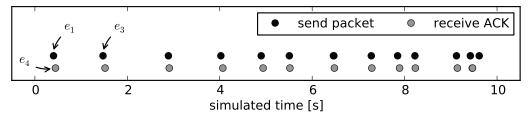

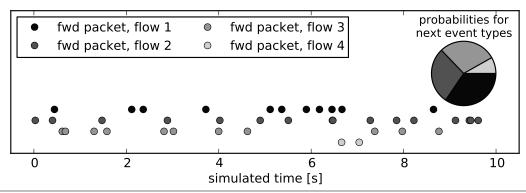

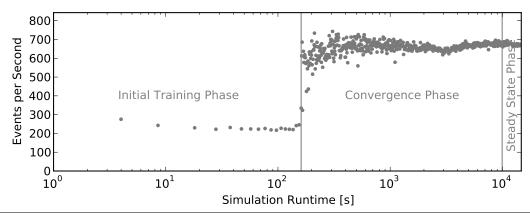

Abstraction is the primary means in simulation to limit model complexity. An abstract model focuses only on the relevant aspects of a system and ignores the irrelevant ones [GG10]. However, as abstraction is a trade-off between accuracy and complexity, the level of abstraction is naturally limited if a high degree of accuracy is required [JZTB06]. If a (computationally) complex system property is important for capturing the behavior of the system, the corresponding simulation model cannot entirely abstract from this property but instead has to model this property appropriately. For instance, investigating wireless communication systems relies on detailed radio propagation, interference, and signal coding models. Those operations exhibit a significant computational complexity – often exceeding the computational complexity of all other events in a simulation model by orders of magnitude as illustrated in Figure 2.2. In addition, large scale communication systems involving thousands or even millions of entities, such as the Internet or peer-to-peer networks, show characteristics, such as delay, latency, and churn, that cannot be observed in networks of smaller size. Hence, representative simulation models have to comprise a large number of network nodes to accurately reflect the behavior of the entire

**Figure 2.2** Histogram showing the computational complexity and number of occurrences of events in a simulation model of a wireless cellular communication network. The complexity of computing the Signal-to-Interference-plus-Noise Ratio (SINR) for all nodes exceeds the complexity of the other events by orders of magnitude. The model is used to investigate resource allocation algorithms in LTE networks.

system [CNO99, SW05, LGW06]. Since each simulated network node occupies memory and generates events, such large scale models require considerable memory and computational resources [FPP+03, WGLW12].

The direct effects of those extensive resource requirements on the evaluation process are two-fold: i) extensive simulation runtimes due to computation complexity, thereby hindering an efficient design space exploration, and ii) limited size of the simulation model due to memory constraints, thereby limiting researchers to potentially unrealistic scenarios.

Parallelization constitutes a possible solution for both limitations. First, distributing large simulation models over multiple computing nodes, i. e., individual computers in a cluster, allows for utilizing the combined memory of all machines. Thus, the simulated network can scale to a realistic size. Second, utilizing multiple processing units, e. g., Central Processing Units (CPUs), allows for processing complex events in parallel, thus reducing the overall runtime of the simulation. The importance of parallelization is further amplified by the fact that in recent years the speed of an individual CPU core remained relatively constant. Hence, when faced with a prohibitively complex computation problem it is no viable solution anymore to simply wait until next generation of CPUs are powerful enough to handle the problem. Instead, the number of cores in a CPU increases, forcing developers to apply parallel programming techniques [GK06, SMD+10].

# 2.2.2 Approaches to Parallelization

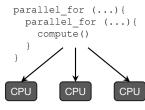

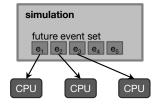

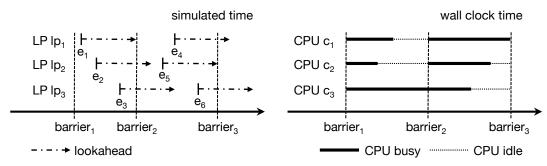

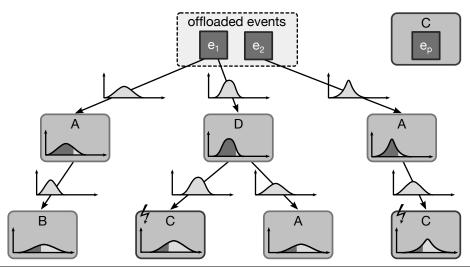

We distinguish three orthogonal approaches to parallelizing a discrete event simulation (see Figure 2.3). Since the workload of a simulation is structured in events, parallelization can target i) the code within the event handlers, denoted as intraevent parallelization, or ii) the execution of multiple events in parallel, referred to as inter-event parallelization. Furthermore, iii) inter-simulation parallelization denotes the execution of entire simulation runs in parallel, each using a different parameter set or random seed.

(a) Intra-event parallelization distributes the workload of a single event to CPUs.

(b) Inter-event parallelization distributes individual events to CPUs.

(c) Inter-simulation parallelization distributes entire simulations to CPUs.

**Figure 2.3** Comparison of three approaches to parallelization: Intra-event, inter-event, and inter-simulation parallelization.

Intra-event Parallelization: The event handlers of a given simulation can generally contain computationally complex code. In this case, parallelizing the code within such event handlers is a viable approach (see Figure 2.3(a)). Specifically, this approach reduces the overall runtime of a simulation by shortening the processing time of complex events through parallelization, yet events are still executed sequentially.

A variety of threading libraries such as Intel Threading Building Blocks [Rei07], OpenMP [DM98], or Cilk [BJK<sup>+</sup>95] provide a rich set of features for parallelizing complex event handlers. For instance, these libraries allow for conveniently parallelizing computations involving loops over arrays of data, as often the case when computing the characteristics of the wireless channel. In case loop iterations are independent, the workload can easily be distributed to multiple worker threads, coordinated by the threading library.

Inter-event Parallelization: Instead of executing one parallelized event at a time, inter-event parallelization aims at processing multiple events of the same simulation in parallel (see Figure 2.3(b)). This approach builds upon the observation that events in a simulation model do not necessarily interfere or depend on each other. For example, handling a network packet in the local protocol stack at two separate nodes is inherently independent. Thus, the fundamental idea of inter-event parallelism is to automatically identify such independent events which are suitable for parallel execution.

Inter-simulation Parallelization: In contrast to inter- and intra-event parallelization, inter-simulation parallelization is a nearly trivial approach to parallelization. It relies on the fact that individual simulation runs with different parameters and seeds are inherently independent, thus allowing for parallel execution (see Figure 2.3(c)). Since thorough evaluation studies typically investigate a given parameter space, this parallelization scheme is in fact widely used – particularly on computing clusters.

The efficiency of intra-event parallelism heavily depends on the workload characteristics of the given simulation model. For example, in simulation models of large scale peer-to-peer networks, the complexity of each event is negligible, but the multitude of events creates a large computational load. Thus, intra-event parallelism is not suitable for such models, hence lacking general applicability. Moreover, if only a

subset of events in a simulation model possess reasonable complexity, the overall reduction in runtime is limited by the fraction of runtime these events contribute to the total simulation runtime. This observation follows directly from Amdahl's Law [Amd67].

Most importantly, intra-event parallelism requires solid knowledge and experience to (re-)structure a given event handler, i.e., algorithm, such that it supports efficient parallel execution. Additionally, every event handler needs to be modified manually by the model developer. Instead, in inter-event parallelization the burden is on the simulation framework to identify parallelizable events while the modeler can focus on the semantics of the model. Consequently, inter-event parallelization is model agnostic.

Finally, inter-simulation parallelization exhibits two drawbacks: First, it does not reduce the runtime of individual simulation runs, thereby hindering rapid prototyping. Second, to fully utilize a multi-core computer, we need to run one simulation instance per CPU. However, the memory requirements of large scale simulation models might prevent running a sufficiently large number of instances on a multi-core computer.

In conclusion, intra-event parallelization lacks general applicability while inter-simulation parallelization does not improve the runtime of individual simulation runs. Because of these limitations, inter-event parallelization constitutes the primary approach to parallel discrete event simulation. As a result, we focus entirely on interevent parallelism in the remainder of this thesis.

# 2.2.3 Challenges of Parallel Event Execution

Recall from Section 2.1.2 that a sequential discrete event simulation is causally correct if all events execute in monotonically increasing timestamp order. It is crucial that a parallel simulation fulfills this correctness requirement as well to retain its applicability as a deterministic evaluation tool. At the same time, parallel discrete event simulation aims for increasing simulation performance by executing events in parallel. Hence, the key challenge of parallel discrete event simulation is maintaining the correctness of the simulation while maximizing simulation performance.

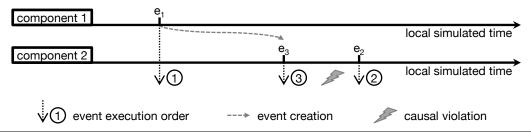

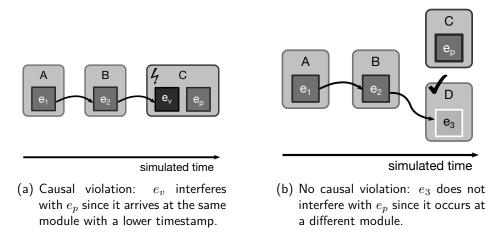

To illustrate that this challenge is indeed non-trivial, consider a naïve approach to parallelization. The simple approach iteratively assigns all events  $e \in F$  in the FES to the available processing units. We consider a simple example shown in Figure 2.4 to illustrate that this approach however cannot guarantee causal correctness, i. e., a monotonically increasing simulated time:

Assume a simulation model which is split into multiple components  $c_1$  and  $c_2$ , in accordance with common software engineering practice. Let furthermore each component maintain an own local virtual time  $t_{c_1}$  and  $t_{c_2}$ . Assume moreover two events  $e_1, e_2 \in F \subseteq E$  with  $t(e_1) < t(e_2)$ . According to our simple parallelization approach, we execute  $e_1$  and  $e_2$  in parallel on two separate CPUs. Thus, the local time of  $c_i$  advances to  $t(e_i), i \in \{1, 2\}$  according to the general execution model of discrete event simulation. In general, the event handler of  $e_1$  at  $c_1$  can create a new event  $e_3$  with  $t(e_1) < t(e_3) < t(e_2)$ , scheduled for execution at component  $c_2$ . However,

**Figure 2.4** Naïve, i.e., unsynchronized, parallel event execution cannot guarantee causal correctness: Processing  $e_2$  before  $e_3$ , which is created by  $e_1$  and hence arrives later than  $e_2$  in the FES, results in a causal violation because  $t(e_3) < t(e_2)$ .

executing  $e_2$  at  $c_2$  already set the local time of  $c_2$  to  $t(e_2)$  which is later than  $t(e_3)$ . Consequently, executing  $e_3$  sets the local time back to  $t(e_3)$ , thereby resulting in a causal violation, i.e., out-of-order event execution.

We conclude from this example that parallelization needs to synchronize and coordinate parallel event execution to achieve causally correct simulation execution. To solve this challenge, parallel discrete event simulation employs specific modeling concepts and synchronization algorithms, which we discuss in the next section.

# 2.3 Concepts of Parallel Discrete Event Simulation

This section introduces the fundamental concepts underlying parallel discrete event simulation. Specifically, we first introduce schemes for partitioning a simulation model, followed by a formal definition of causal correctness. Finally, we briefly discuss two classes of synchronization schemes and distinguish three different event execution environments.

# 2.3.1 Workload Partitioning

A parallel simulation needs to partition the workload of a simulation run to make use of multiple processing units. In the following, we briefly sketch three different partitioning schemes.

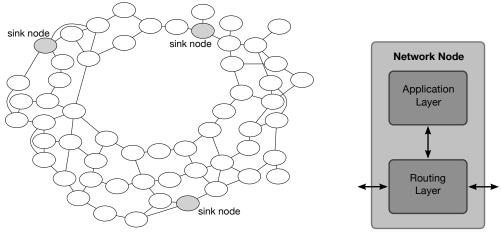

Space-parallel Partitioning: The de facto standard partitioning scheme in PDES is space-parallel partitioning [Fuj90a]. This scheme splits a simulation model into groups of simulated entities which in turn form a partition. In case of network simulations, these entities correspond to network nodes and their subcomponents such as protocol stacks, network cards, routing tables, etc. Since simulation models typically exhibit a modular structure corresponding to those entities, this scheme is generally applicable.

In a special case of space-parallel partitioning, a simulation model is distributed across different simulation frameworks, called *federates*. The purpose of this approach is to couple specialized simulators to take advantage of their particular features and simulation models. For instance, in order to evaluate the hardware design of a network router, a network simulation can simulate the

(a) Space-parallel partitioned model of a wired network. Clusters of local nodes map to partitions.

(b) Channel-parallel partitioned model of a cellular network. Nonneighboring cells map to partitions.

(c) Time-parallel partitioned simulation run. Different periods of the simulated time map to partitions.

**Figure 2.5** Overview of space-, channel-, and time-parallel partitioning. In all three examples, the workload is distributed over three partitions.

surrounding network and its traffic while a hardware simulator models the internals of the router. However, despite a different terminology (federates instead of partitions), the parallelization challenges and corresponding solutions are equivalent. Hence, we do not explicitly consider federated simulation in the remainder of this thesis.

A key goal of the partitioning process is to achieve an equal distribution of workload over all partitions while limiting inter-partition communication. Thus, depending on the properties of a given simulation model, assigning entities to partitions follows different strategies. For instance, large wired networks, such as the Internet, lend themselves to partitioning along backbone links as shown in Figure 2.5(a). Assuming that the majority of network traffic is between local nodes, this strategy maps clusters of local nodes to partitions in order to minimize cross-partition communication. In contrast, small and local wireless ad-hoc networks do not posses such backbone links. Instead, partitioning such networks often bases on the simulated geographic location of a network node.

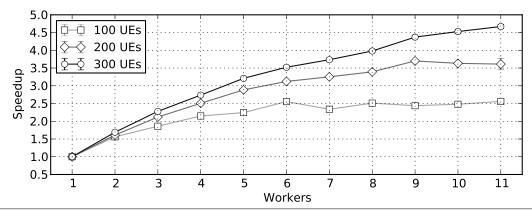

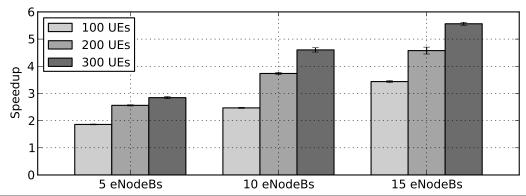

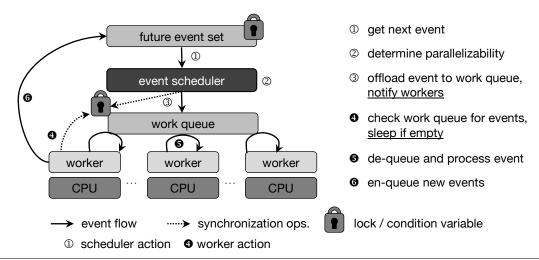

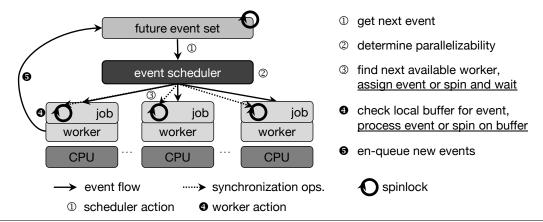

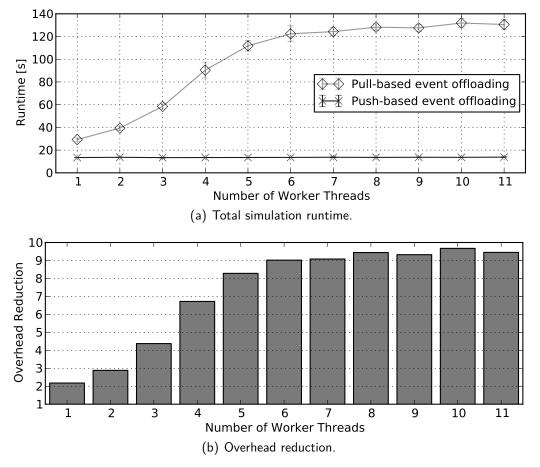

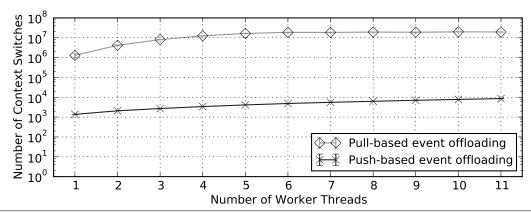

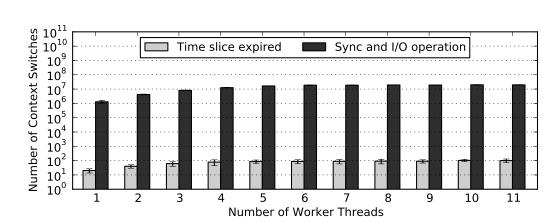

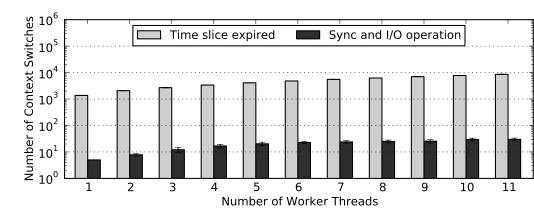

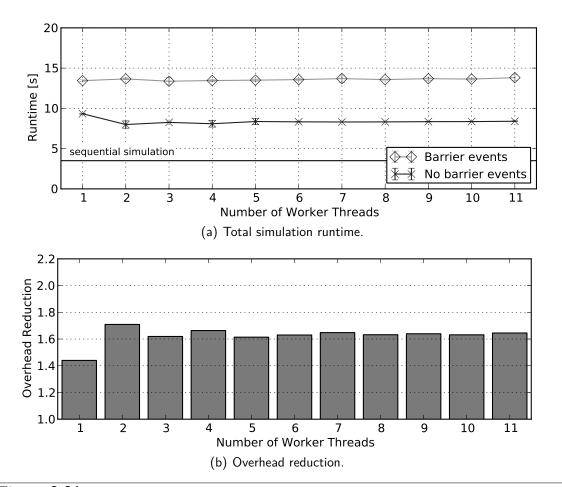

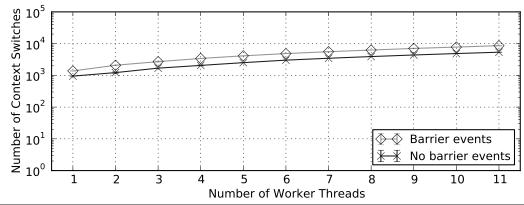

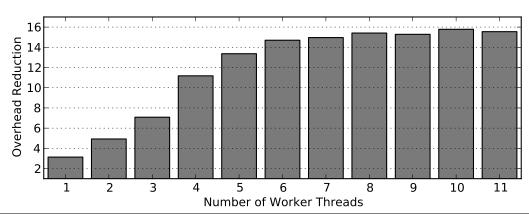

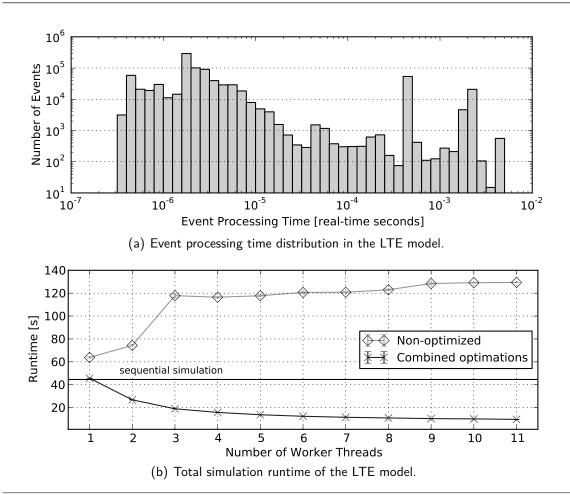

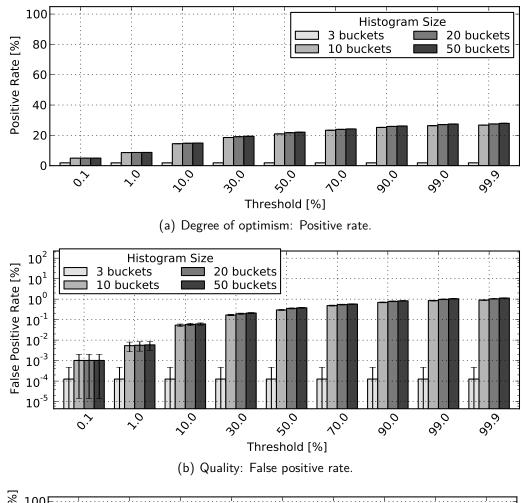

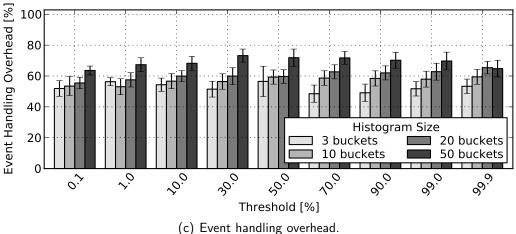

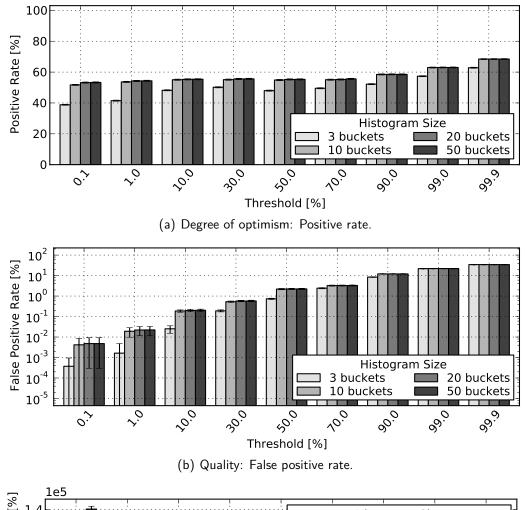

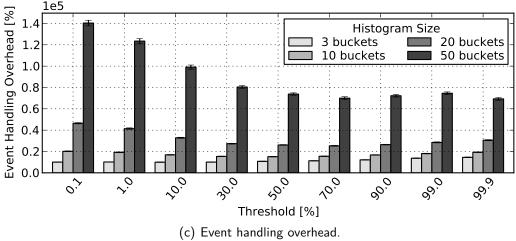

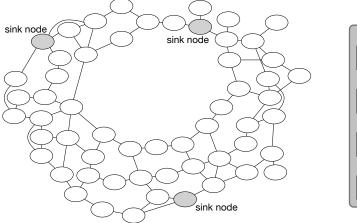

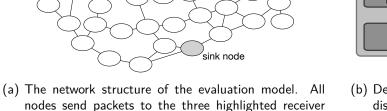

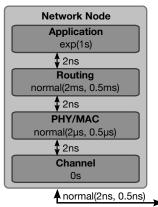

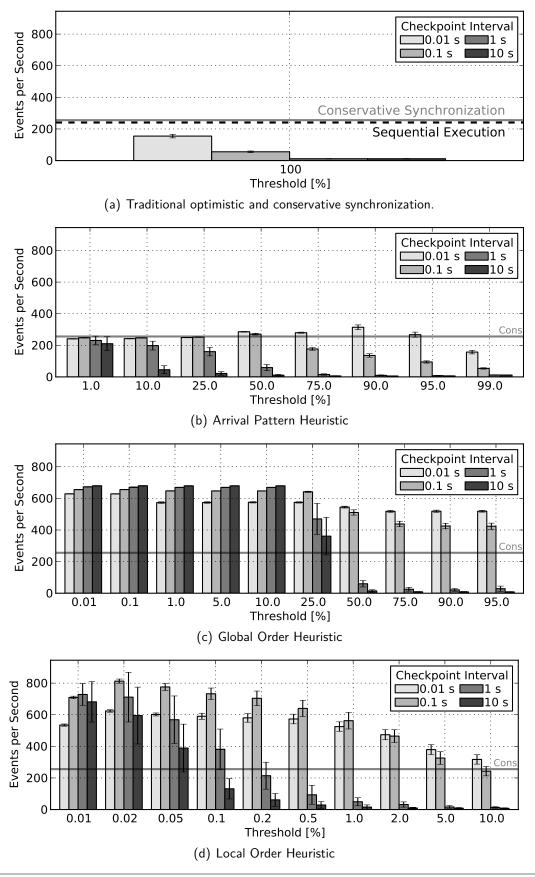

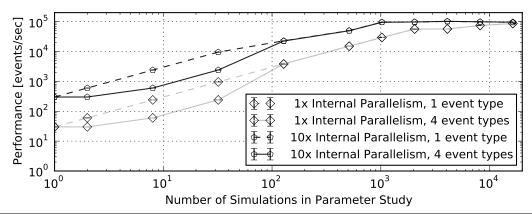

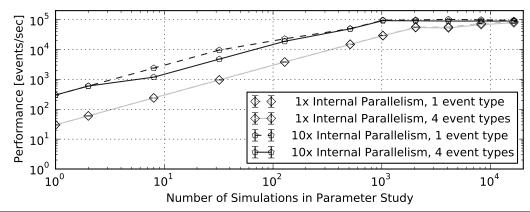

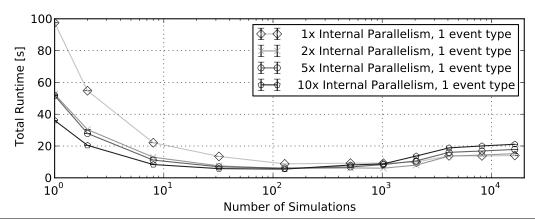

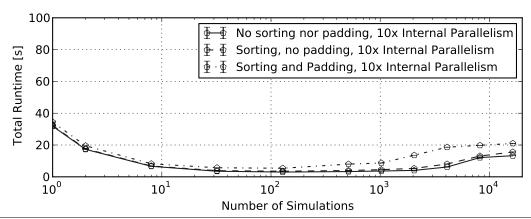

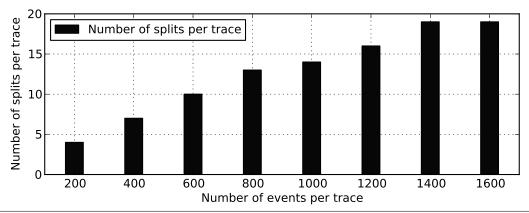

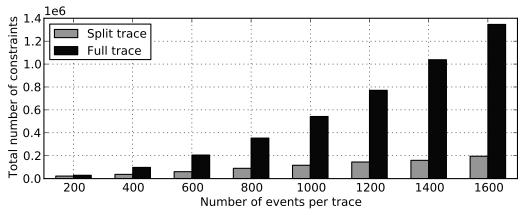

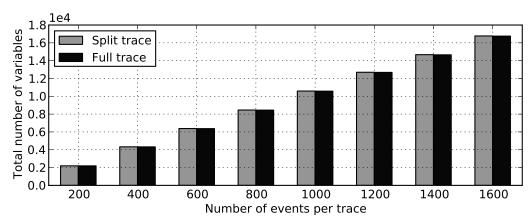

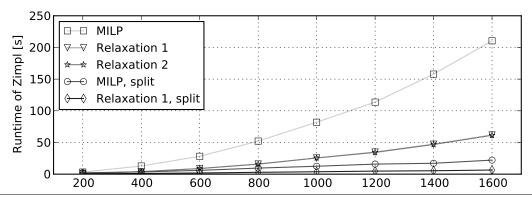

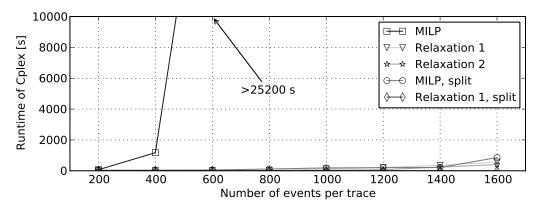

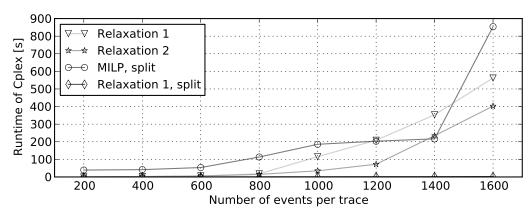

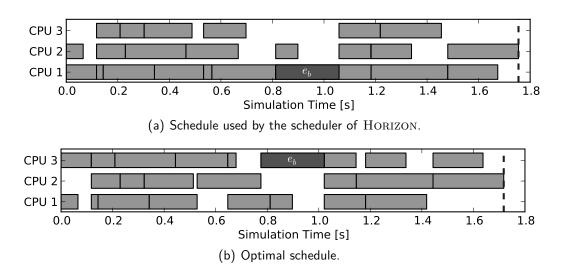

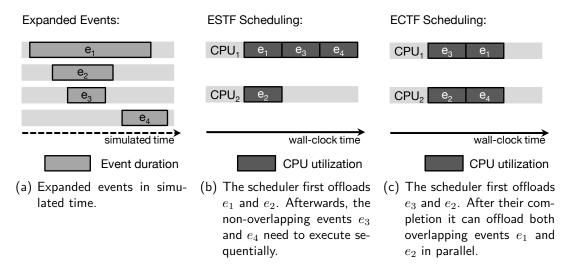

Channel-parallel Partitioning: A partitioning scheme specific to network simulation is channel-parallel partitioning [LA96, LA97]. The scheme leverages the fact that wireless communication on non-interfering channels is independent. It partitions a simulated network according to non-interfering channels and forms clusters of network nodes communicating on the same channel. This scheme finds application primarily in simulations of cellular communication systems such as GSM, UMTS, or LTE in which neighboring cells use non-interfering channels (see Figure 2.5(b)). Nevertheless, it is not well suited when neighboring channels overlap such as in IEEE 802.11g/n or if the whole network transmits on the same channel, for instance in Code Division Multiple Access (CDMA) systems.